等離子預(yù)處理作用

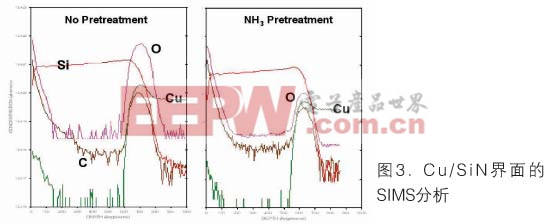

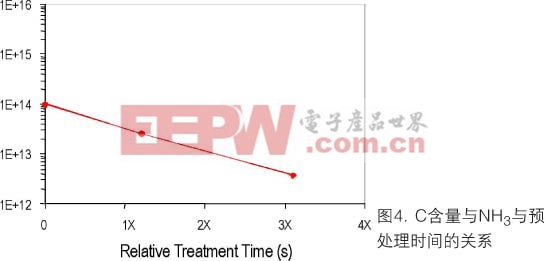

為了了解等離子處理對Cu/SiN界面的作用���,在PECVD系統(tǒng)中于淀積SiN體薄膜前有和沒有預(yù)處理情況下淀積SiN薄膜。通過用SIMS測量Cu和SiN界面污染����,研究等離子預(yù)處理的作用。實(shí)驗(yàn)數(shù)據(jù)說明����,淀積SiN體薄膜前用NH3處理可顯著減少Cu和SiN界面處的O和C含量(圖3)。增加預(yù)處理時(shí)間也可使O和C含量減少��,見圖4和圖5��,這表明NH3預(yù)處理是去除有機(jī)污染和減少到Cu的Cu-O的有效方法��。

評論