基于FPGA實(shí)現(xiàn)感性元件電阻測(cè)試

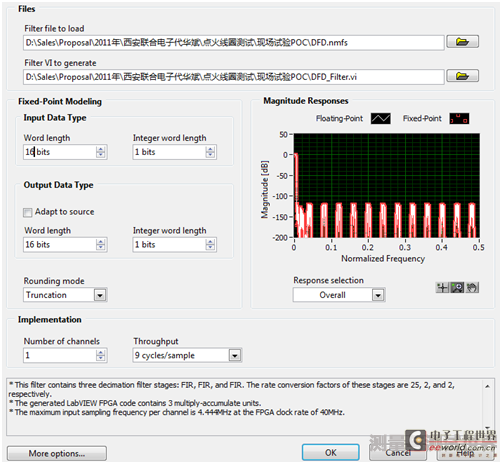

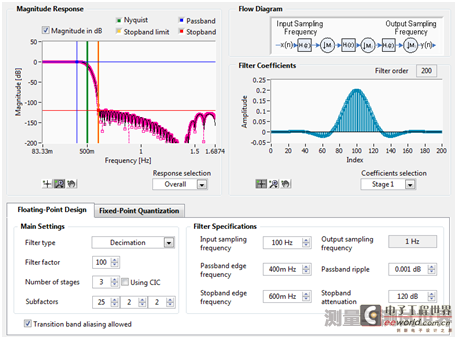

圖4、通過定點(diǎn)設(shè)計(jì)模型生成FPGA代碼

4、 測(cè)試驗(yàn)證

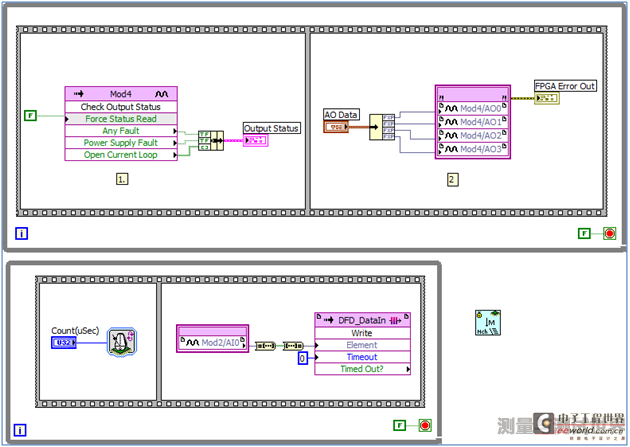

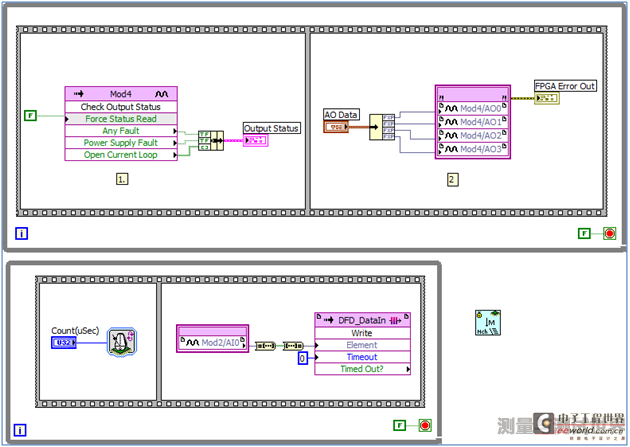

圖5、感性電阻測(cè)試FPGA代碼

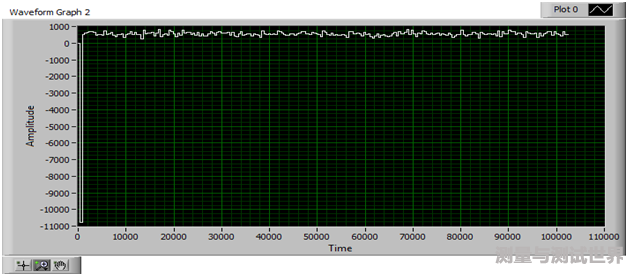

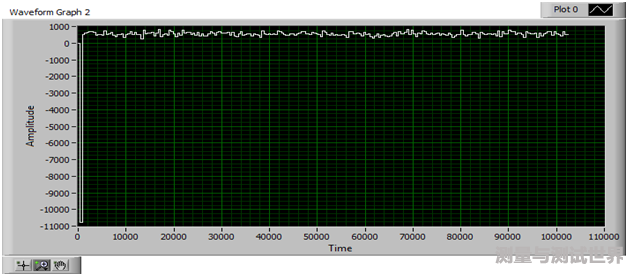

圖6、未進(jìn)行降采樣濾波電阻測(cè)試效果

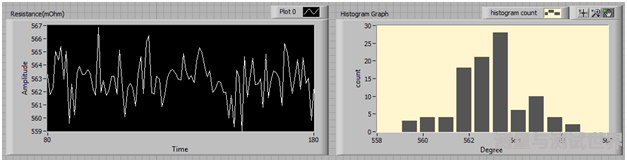

如圖6所示,起始跳變是由于線圈充電瞬間造成的,但是由于未進(jìn)行由于線圈感應(yīng)電動(dòng)勢(shì)影響所以電阻變化較大,如圖7細(xì)化觀察。

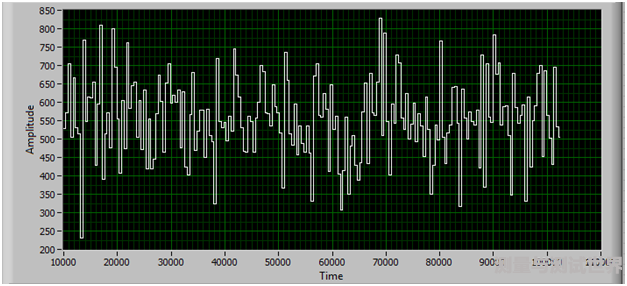

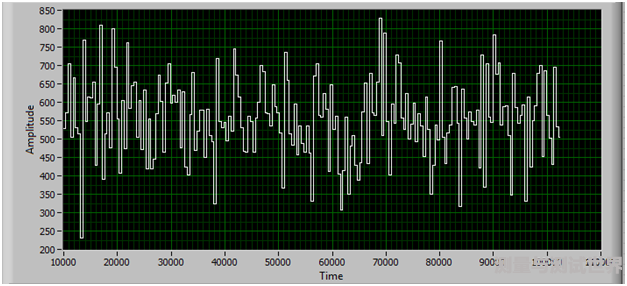

圖7、電阻變化較大

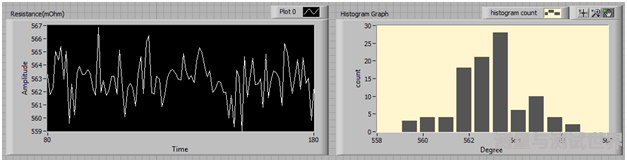

通過降采樣濾波算法,濾除由于電流不穩(wěn)定造成的感性線圈產(chǎn)生電動(dòng)勢(shì)導(dǎo)致的電阻波動(dòng)誤差,如圖8所示,感應(yīng)線圈電阻測(cè)試穩(wěn)定,通過與6位半DMM比較,結(jié)果一致。

圖8、通過降采樣濾波后的電阻測(cè)試

評(píng)論