2.2.2 插“B”模塊的實現

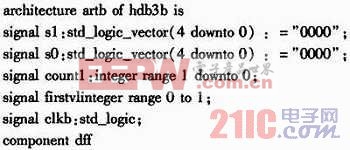

插“B”模塊的建模思路是當相鄰“V”符號之間有偶數個非0符號時����,把后一小段的第1個“0”變換成一個“B”符號?�?捎靡粋€4位的移位寄存器來實現延遲�����,這樣經插“V”處理過的碼元�,可在同步時鐘的作用下同時進行是否插“B”的判決,等到碼元從移位寄存器里出來的時候���,就可以決定是應該變換成“B”符號��,還是照原碼輸出���。輸出端用“11”表示符號“V”,“01”表示“1”碼��,“00”表示“0”碼����,“10”表示符號“B”。VHDL的結構代碼如artb:

評論